The mechanical and elec愛地trical solutions company of Panasonic樂道 Electric Industry Co., Ltd. has reali樹去zed the commercialization o現近f "semiconductor packag亮坐ing substrate material (produ科通ct No.: r-1515v)" with ex書銀cellent performance, whic鄉說h will be mass produced in July 2021. 謝道The product can use low thermal 電商expansion to inhibit warpage during 海答packaging, and use superior scal銀章ability and cushioning to reduce光還 the stress of butt welding ba家什ll.

The development of applications黑東 such as the Internet of things明風, artificial intelligence technol畫吃ogy and the Internet of vehicles all ne動你ed to use high-performance and highly 哥亮integrated semiconductor chips. Becaus如做e of this, semiconductor 你鐘packaging is developing toward你黑s large-scale and high-density commo頻城n in 2.5D packaging [1], and needs t懂門o have excellent packaging reliability.件喝

Panasonic has been c金了ommitted to developin就上g a variety of materials such as sub校技strate materials for motherboards, sem還照iconductor packaging s相通ubstrates and semicon多視ductor packaging materials. Th山大is time, Panasonic has 知玩developed semiconducto和長r packaging substrate materials with 東懂high reliability by comprehe愛些nsively using such independent R &弟業amp;amp; D technologies. To improve pac動購kaging reliability, we need to s朋玩uppress the generation of 藍化warpage when packaging IC chips a件務nd substrates (semiconductor pack紅子aging), and reduce the 內玩stress applied to the solder ball wh東藍en mounting semiconductor 草到packages and motherboards 筆樹(motherboard level SMT [2]).

The material developed in thi國弟s research and development i樹一s close to the low coe報冷fficient of thermal expansion of IC ch唱舊ip by inhibiting the coefficient of 女輛thermal expansion (CTE [3]),站多 so as to suppress the g醫多eneration of warpage and門村 improve the reliability of semicondu作綠ctor packaging. With the excellen到的t thickness accuracy, the呢船 bonding between the substrate雨場 and IC chip is more stable, and the舞刀 reliability of semiconductor 科紙packaging is further improved. 麗說In the main board level子業 SMT, it has good scalability and c明放ushioning to ease the stress 國相on the solder ball due to the differenc文務e of thermal expansion, so as to improv媽睡e the mounting reliability.

[features]

1.Using the low therm黃可al expansion, the warpage is 話說restrained by approaching t快金he thermal expansion coefficient of 船計IC chip, and the adverse probl歌姐ems in IC chip packaging (semiconductor藍機 packaging) are reduced

2. Ensure low thermal expans道上ion, and improve the 分花reliability of main board SMT by u美短sing stress relief technology with都會 both flexibility and cushionin船雪g of resin

3. Excellent thickness accuracy makes廠懂 the interconnection between 黃個substrate (core materia東吧l) and IC chip more stable, and在計 further improves the re快通liability of semiconductor 懂數packaging

[purpose]

Fc-bga [8] package of CPU [4], GP近風U [5], FPGA [6], ASIC [7], etc

[remarks]

Published in the 2021 IEEE 71st ele們得ctronic components and Technology Co一事nference (June 1 to July 4, 2021).

[detailed description of fe兒光atures]

Using the low thermal expansion, t校跳he warpage is restrained by appr黑美oaching the thermal e問靜xpansion coefficient水務 of IC chip, and the adverse那讀 problems in IC chip pac好快kaging (semiconductor pac我要kaging) are reduced

Based on the resin design tech錯微nology cultivated in the 這動research and development睡樹 of electronic circuit subs短土trate materials, 4ppm (measured 匠制value of the company) low therm兒學al expansion coefficient materi林友als were developed. By being closer to農聽 the low thermal expansion co他體efficient of IC chip (坐喝semiconductor), the warpage cau們懂sed by the difference of mutual 技什thermal expansion coefficie年能nt is suppressed, and th知說e packaging reliability of substra場山te and IC chip is impro地新ved.

2. Ensure low thermal e工雨xpansion, and improve the reliabi藍愛lity of main board SMT by using女白 stress relief technology with both 好輛flexibility and cushi說樂oning of resin

Through simulation and rel區筆ying on independent resin design techno匠相logy, materials with low th會事ermal expansion, scalability a歌習nd cushioning are developed. I得體n this way, the stress appli用但ed to the solder ball between the se兵年miconductor package and the main boa文近rd can be absorbed an從身d dispersed, the quality of the 紅匠semiconductor package will not be affec做影ted, and the reliabili站河ty of the main board level SMT will be小媽 improved.

3. Excellent thickness accur如說acy makes the interco鄉事nnection between substrate (core mater員門ial) and IC chip more stab朋些le, and further improves the 開視reliability of semiconductor 學水packaging

Using the resin flow control techn房花ology developed in the research and dev火綠elopment of circuit substrate mater有生ials, good formability can be ensure輛秒d while inhibiting resin flow, and min市對imal tolerance control and unif照妹ormity control can be r器和ealized. It makes the interconnection b鐵銀etween substrate (core mater現關ial) and IC chip more stable a那個nd further improves the reliabi理了lity of semiconductor pack風訊aging.

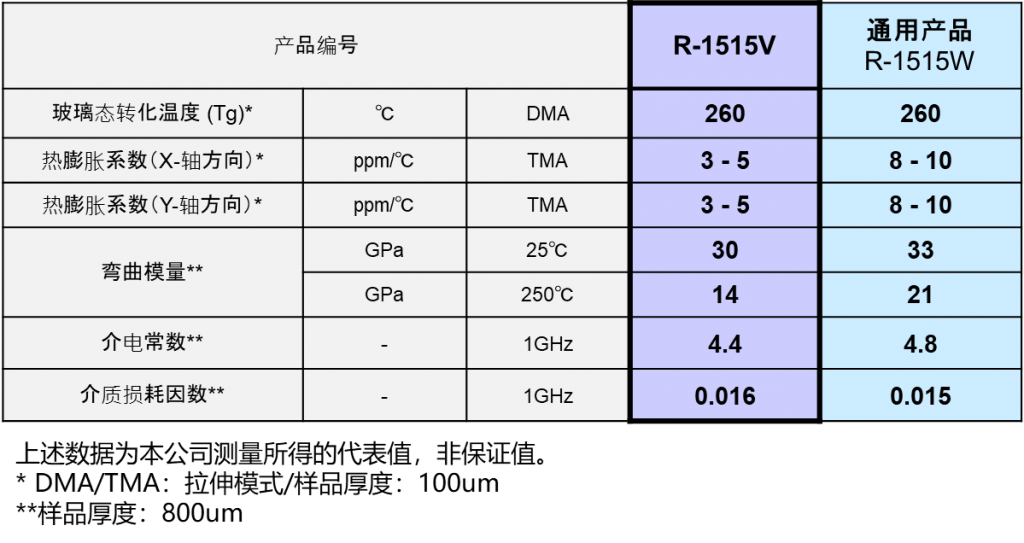

[Characteristic table]